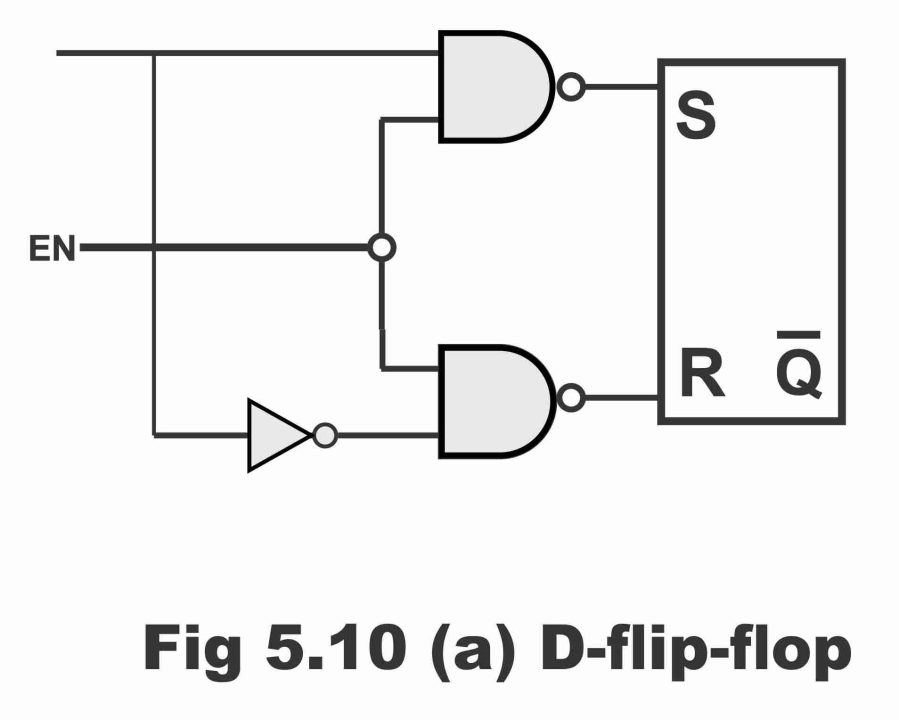

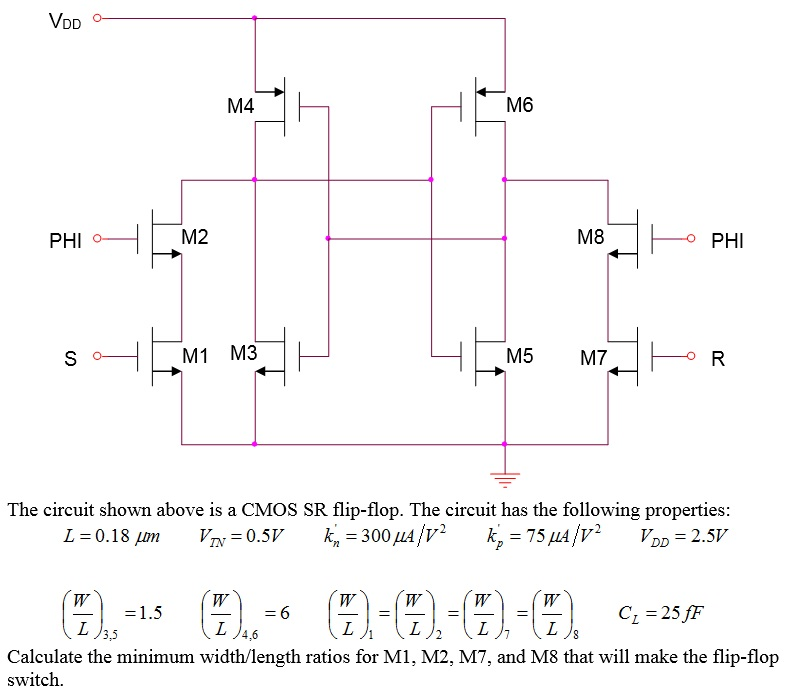

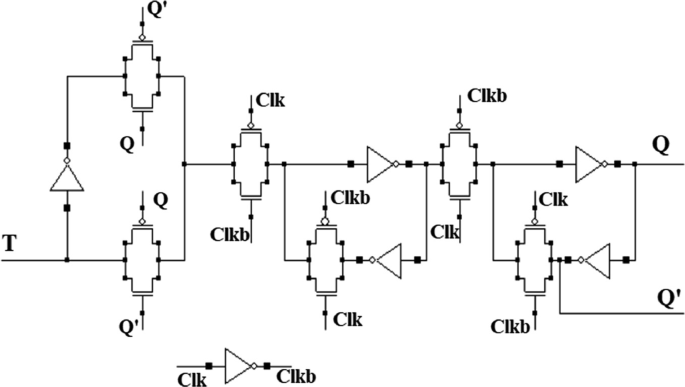

Figure 4 from Layout Design of 5 Transistor D Flip Flop for Power and Area Reduction and Performance Comparison in Different Scaling Technologies | Semantic Scholar

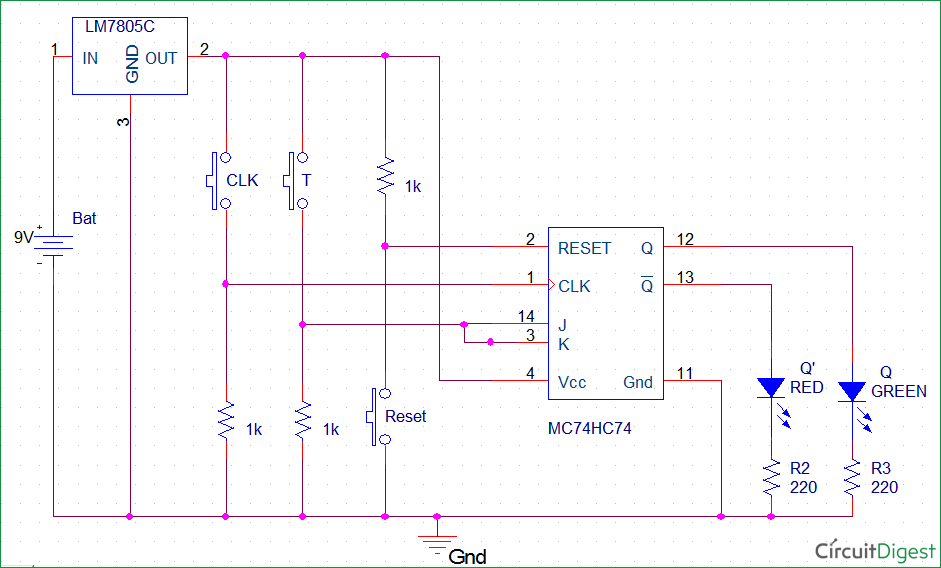

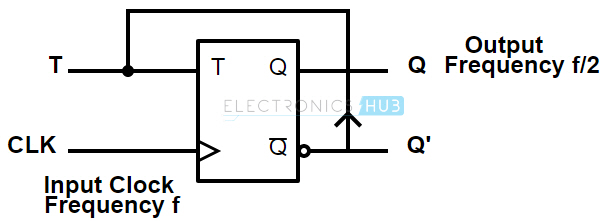

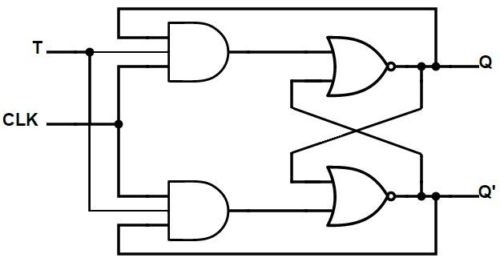

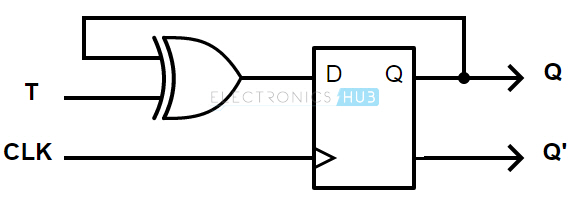

Design and Comparison of Low-Power, High-Speed T Flip Flop, and 4-Bit Asynchronous Counter Using Various Design Techniques | SpringerLink